| <b>1(a).</b> The stored program concept uses the Fetch-Decode-Execute cycle to get the next instruction from memory and then execute it. |

|------------------------------------------------------------------------------------------------------------------------------------------|

| Describe what happens during the <b>fetch</b> stage of the Fetch-Decode-Execute cycle.                                                   |

| You should state the different registers and buses that are used in your answer.                                                         |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

| [4]                                                                                                                                      |

| (b). One of the instructions that may be fetched and executed as part of this cycle is a branch instruction.                             |

| State the name of the register that would be altered in the <b>execute</b> phase during a branch instruction.                            |

| [1]                                                                                                                                      |

| (c). Three ways of improving the performance of a CPU are increasing the clock speed, adding more cores and using pipelining.            |

| Explain how pipelining improves the performance of a CPU.                                                                                |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

|                                                                                                                                          |

| [3]                                                                                                                                      |

[5]

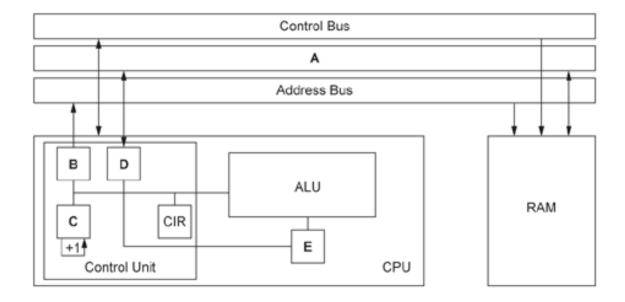

2. Here is a diagram of a computer system.

Identify each of the labelled components in this computer system.

| Α |  |

|---|--|

| В |  |

| С |  |

| D |  |

| E |  |

**3.** Most modern computers are designed using Von Neumann Architecture. However, in some cases Harvard Architecture may be preferred.

Discuss the difference between Von Neumann Architecture and Harvard Architecture.

You should refer to the following in your answer:

- · the different approaches each architecture takes to storing instructions and data

- the benefits of using a Von Neumann Architecture approach

- the benefits of using a Harvard Architecture approach.

| 1.1.1. Structure and Function of the Processor                                                                                                                                                                                                                                | PhysicsAndMathsTutor.con                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                               | [9]                                                                              |

| <b>4.</b> OCRSystems are designing a new CPU for a computer system that the video rendering process is when the video is exported. This is who separate video elements together to form the final video.  Describe <b>two</b> factors that affect the performance of the CPU. | nt will be used for video rendering. Part of en the computer combines all of the |

|                                                                                                                                                                                                                                                                               |                                                                                  |

| 1                                                                                                                                                                                                                                                                             |                                                                                  |

|                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                               |                                                                                  |

| 2                                                                                                                                                                                                                                                                             |                                                                                  |

|                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                                                                                                                                               | [4]                                                                              |

|                                                                                                                                                                                                                                                                               |                                                                                  |

| proce | essor.                                                                                                                                                           |     |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Give  | <b>two</b> features of a replacement processor that would increase the typical performance of the computer.                                                      |     |

| 1     |                                                                                                                                                                  |     |

|       |                                                                                                                                                                  |     |

| 2     |                                                                                                                                                                  |     |

|       |                                                                                                                                                                  |     |

|       | [2]                                                                                                                                                              |     |

|       | The processor contains registers including the accumulator and the program counter. The contents of the ters are modified during the Fetch-Decode-Execute cycle. | ese |

| i.    | Describe how the accumulator is used during the Fetch-Decode-Execute cycle.                                                                                      |     |

|       |                                                                                                                                                                  |     |

|       |                                                                                                                                                                  |     |

|       |                                                                                                                                                                  |     |

|       |                                                                                                                                                                  | [2] |

| ii.   | Describe how the program counter is used during the Fetch-Decode-Execute cycle.                                                                                  |     |

|       |                                                                                                                                                                  |     |

|       |                                                                                                                                                                  |     |

|       |                                                                                                                                                                  |     |

|       |                                                                                                                                                                  | [2] |

| iii.  | State the name of <b>three</b> other registers that are used during the Fetch-Decode-Execute cycle.                                                              |     |

| 4     |                                                                                                                                                                  |     |

| 1     |                                                                                                                                                                  |     |

| _     |                                                                                                                                                                  |     |

| 2     |                                                                                                                                                                  |     |

| 3     |                                                                                                                                                                  |     |

| J     |                                                                                                                                                                  |     |

| _     |                                                                                                                                                                  |     |

**5(a).** A charity is concerned that the performance of a computer is not sufficient and wishes to replace the

| A pro        | ocessor uses the Von Neumann architecture.                                                   |     |  |  |  |

|--------------|----------------------------------------------------------------------------------------------|-----|--|--|--|

| i.           | Describe what is meant by the term 'Von Neumann architecture'.                               |     |  |  |  |

|              |                                                                                              |     |  |  |  |

|              |                                                                                              | [2] |  |  |  |

| ii.          | Give <b>one</b> way that the Harvard architecture differs from the Von Neumann architecture. |     |  |  |  |

|              |                                                                                              | [1] |  |  |  |

| <b>6.</b> St | tate why computer systems store data in binary.                                              |     |  |  |  |

|              |                                                                                              | [1] |  |  |  |

| <b>7.</b> Di | ifferent computing devices in Arnold's home use different processor architectures.           |     |  |  |  |

| One          | processor architecture is the Harvard architecture.                                          |     |  |  |  |

| i.           | Describe the Harvard architecture.                                                           |     |  |  |  |

|              |                                                                                              |     |  |  |  |

|              |                                                                                              | [2] |  |  |  |

| ii.          | Arnold has a smart washing machine.                                                          |     |  |  |  |

|              | Explain why the Harvard architecture is suitable for a device like this.                     |     |  |  |  |

|              |                                                                                              |     |  |  |  |

|              |                                                                                              | [2] |  |  |  |

**(c).** A charity uses a desktop computer to record financial donations that it receives. The computer contains a single core, 2.4GHz processor with 2MB cache.

| <b>8.</b> A pro | ogram wri<br>IN | itten using the Little Man Computer instruction set is shown in <b>Fig. 1</b> .                           |     |

|-----------------|-----------------|-----------------------------------------------------------------------------------------------------------|-----|

|                 | ST.             |                                                                                                           |     |

|                 | IN              |                                                                                                           |     |

|                 | ST.             |                                                                                                           |     |

| main            | LD.             | A numone                                                                                                  |     |

|                 | SU              | B numtwo                                                                                                  |     |

|                 | BR              | P pos                                                                                                     |     |

| notpo           | os LD           | A count                                                                                                   |     |

| _               | OU'             | T                                                                                                         |     |

|                 | LD.             | A numone                                                                                                  |     |

|                 | OU.             | T                                                                                                         |     |

|                 | HL              | T                                                                                                         |     |

| pos             | ST.             |                                                                                                           |     |

|                 | LD.             |                                                                                                           |     |

|                 | AD              |                                                                                                           |     |

|                 | ST.             |                                                                                                           |     |

|                 | BR.             |                                                                                                           |     |

| numor           |                 |                                                                                                           |     |

| numty           |                 |                                                                                                           |     |

| one             | DA'             |                                                                                                           |     |

| count           |                 | T Ö                                                                                                       |     |

| Fig. 1          |                 |                                                                                                           |     |

|                 |                 | n Architecture, various registers are used when a program is executed at is meant by the term 'register'. |     |

| ii. I           | Explain h       | ow the accumulator is used when the line BRP pos is executed.                                             | [2] |

|                 |                 |                                                                                                           | [2] |

\_\_\_\_\_[4]

Describe **one** non-graphical use for a GPU.

iii.

|                                                                                              | [2] |

|----------------------------------------------------------------------------------------------|-----|

| 40(a). Amy's pressent makes use of pipeliping during the fotch decade evecute evels          |     |

| <b>10(a).</b> Amy's processor makes use of pipelining during the fetch-decode-execute cycle. |     |

| The processor's pipeline consists of the following stages:                                   |     |

| Fetching the instruction from memory  Paged in a the instruction.                            |     |

| <ul> <li>Decoding the instruction</li> <li>Executing the instruction.</li> </ul>             |     |

|                                                                                              |     |

| Instructions A, B, C and D need to be processed.                                             |     |

| Identify the stage(s) and instruction(s) run during each pipeline below.                     |     |

|                                                                                              |     |

| Pipeline 1                                                                                   |     |

|                                                                                              |     |

|                                                                                              |     |

| Pipeline 2                                                                                   |     |

|                                                                                              |     |

|                                                                                              | ,   |

|                                                                                              |     |

| Pipeline 3                                                                                   |     |

|                                                                                              |     |

|                                                                                              |     |

|                                                                                              |     |

| Pipeline 4                                                                                   |     |

|                                                                                              |     |

|                                                                                              |     |

|                                                                                              |     |

| (b). Explain why pipelining can improve the performance of the processor. |     |  |  |

|---------------------------------------------------------------------------|-----|--|--|

|                                                                           |     |  |  |

|                                                                           |     |  |  |

|                                                                           |     |  |  |

|                                                                           | [2] |  |  |

**11(a).** The table below shows the Little Man Computer instruction set.

| Mnemonic | Instruction   |

|----------|---------------|

| ADD      | Add           |

| SUB      | Subtract      |

| STA      |               |

| LDA      | Load          |

|          | Branch always |

| BRZ      |               |

| BRP      |               |

| INP      | Input         |

| OUT      | Output        |

|          | End program   |

| Complete the table above to show the missing mnemonics and instructions.                                                                                                           | [5]            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| ( <b>b).</b> Write a program using the Little Man Computer instruction set that will allow a user to input the character of the two numbers. The program should loop continuously. | wo numbers and |

|                                                                                                                                                                                    |                |

|                                                                                                                                                                                    |                |

|                                                                                                                                                                                    |                |

|                                                                                                                                                                                    |                |

|                                                                                                                                                                                    |                |

|                                                                                                                                                                                    |                |

|                                                                                                                                                                                    |                |

| 1.1.1. Structure and Function of the Processor                                                               | PhysicsAndMathsTutor.com |

|--------------------------------------------------------------------------------------------------------------|--------------------------|

|                                                                                                              |                          |

|                                                                                                              |                          |

|                                                                                                              |                          |

|                                                                                                              |                          |

|                                                                                                              |                          |

|                                                                                                              |                          |

|                                                                                                              |                          |

|                                                                                                              |                          |

|                                                                                                              |                          |

|                                                                                                              | [6]                      |

| <b>12(a).</b> A company produces CPUs for desktop and laptop computers. Each CPU is de Neumann Architecture. |                          |

| Describe what is meant by the term 'Von Neumann Architecture'.                                               |                          |

|                                                                                                              |                          |

|                                                                                                              |                          |

|                                                                                                              | ro1                      |

|                                                                                                              | [2]                      |

|                                                                                                              |                          |

В

С

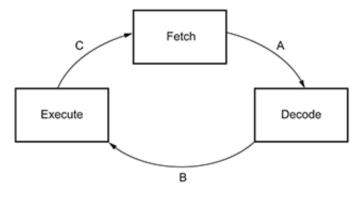

(b). A CPU will repeatedly run the Fetch-Decode-Execute-cycle shown in Fig. 1.

Fig. 1

| i.  | Describe what happens during the 'Fetch' stage shown in <b>Fig. 1</b> .  You should refer to the use of specific registers in your answer. |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------|----|

|     |                                                                                                                                            |    |

|     |                                                                                                                                            |    |

|     |                                                                                                                                            |    |

|     |                                                                                                                                            |    |

|     |                                                                                                                                            | [4 |

| ii. | A CPU may need to stop running the Fetch-Decode-Execute-cycle in order to handle an interrupt.                                             |    |

|     | Tick <b>one</b> box to indicate where in <b>Fig. 1</b> an interrupt would be handled.                                                      |    |

| ^   |                                                                                                                                            |    |

[1]

**END OF QUESTION PAPER**